ISRO 2011 EC SET A

1. In an amplitude modulated system if the total power is 600 W and the power in the carrier is 400W, the modulation index is

a. 0.5

b. 0.75

c. 0.9

d. 1

Solution:

PSide band = PTotal

– Pcarrier

PSide

band = 600 - 400 = 200 W

Solving we get µ = 1

Answer: Option d

2. The channel capacity under the Gaussian noise environment for a discrete memoryless channel with a bandwidth of 4 MHz and SNR 31 is

a. 20 Mbps

b. 4 Mbps

c. 8 Kbps

d. 4 Kbps

Solution:

Channel capacity = C=B log2(1+

SNR)

= 4 M log2(1+31)

= 4 M x 5 = 20 Mbps

Answer: Option: a

3. In satellite communication, frequency modulation is used because satellite channel has

a. High Modulation index

b. Small bandwith and negligible noise

c. Large bandwidth and severe noise

d. Maximum Bandwidth and Minimum noise

Answer: Option d

4. For a 3-µm diameter optical fiber with core and cladding indexes of refraction of 1.545 and 1.510 respectively. The cut off wavelength is

a. 2.3 µm

b. 1.29 µm

c. 1.5 µm

d. 3.24 µm

Solution:

= 1.2808 µm

Answer: option b

Solution:

Answer: Option b

A Process contains only sequential statements.

Answer : option b

212 = 4096 bytes = 4Kbytes

Answer: Option d

Aswer: option d

Thread: the primitive that can execute code. It contains an Instruction pointer and sometimes has its own stack.

Process: An environment in which one or several threads run.

Kernel: Run time OS- takes care of thread scheduling.

Answer: Option d

The ouput toggles when J=K=1.

Answer: Option d

Answer: Option d

Answer: Option c

Answer: Option c

Answer: Option b

Answer: Option c

Answer: Option a

Answer: Option b

Answer: Option c

Answer: Option a

Answer: Option a

Answer: Option d

Answer: Option b

Answer: Option a

Answer: Option c

Answer: Option a

Answer: Option b

Answer: Option b

Answer: Option b

Answer: Option d

Answer: Option a

Answer: Option d

Answer: Option a

Answer: Option c

Answer: Option b

Answer: Option b

Answer: Option b

Answer: Option c

Answer: Option b

Answer: Option c

Answer: Option a

Answer: Option b

Answer: Option a

Answer: Option c

Answer: Option c

Answer: Option d

Answer: Option b

3. In satellite communication, frequency modulation is used because satellite channel has

a. High Modulation index

b. Small bandwith and negligible noise

c. Large bandwidth and severe noise

d. Maximum Bandwidth and Minimum noise

Answer: Option d

4. For a 3-µm diameter optical fiber with core and cladding indexes of refraction of 1.545 and 1.510 respectively. The cut off wavelength is

a. 2.3 µm

b. 1.29 µm

c. 1.5 µm

d. 3.24 µm

Solution:

= 1.2808 µm

Answer: option b

5. A 12 bit ADC is

operating with a 1 µs clock period and total conversion time is seen to be 14 µs

always. The ADC must be of the type

a) Flash

b) Counting type

c)

Integrating type

d) Successive Approximation type

Answer: Option b

A Process contains only sequential statements.

Answer : option b

212 = 4096 bytes = 4Kbytes

Answer: option d

A resistance in parallel with an indeal current source.

Answer: Option b

The dominant mode has lowest cutoff frequency and hence highest cutoff wavelength.

Answer: Option d

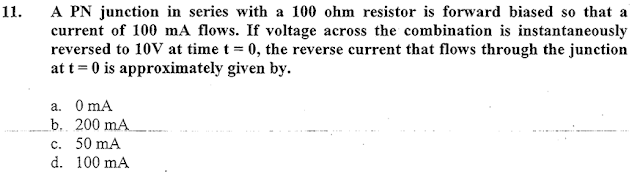

The reverse recovery time involves a diode switching from FB to RB. Reverse recovery time will be of several microseconds. Therefore at t=0, the diode would not have recovered from forward bias condition. Hence current will be same as 100 mA.A resistance in parallel with an indeal current source.

Answer: Option b

The dominant mode has lowest cutoff frequency and hence highest cutoff wavelength.

Answer: Option d

Answer: Option d

Aswer: option d

Thread: the primitive that can execute code. It contains an Instruction pointer and sometimes has its own stack.

Process: An environment in which one or several threads run.

Kernel: Run time OS- takes care of thread scheduling.

Answer: Option d

Answer: Option c

Total frequency = 3.6k + 3 x (1.2k) = 7.2kHz

Sampling frequency = 2 x 7.2 k = 14.4 Khz

Answer: Option b

An Addition of 6-dB improvement in SNR is obtained for each bit added to the PCM word.

6.02 x n = 6.02 x 2 = 12.04 = increase by 12 dB

Answer: Option b

QPSK is mostly used in digital data.

Answer: option d

Answer: Option a

Clock

|

J

|

K

|

Qn

|

Q’n

|

Qn+1

|

Q’n+1

|

0th clock

|

0

|

1

|

0

|

1

|

1

|

0

|

1st clock

|

1

|

1

|

1

|

0

|

0

|

1

|

2nd clock

|

0

|

1

|

0

|

1

|

1

|

0

|

3rd clock

|

1

|

1

|

1

|

0

|

0

|

1

|

4th clock

|

0

|

1

|

0

|

1

|

1

|

0

|

5th clock

|

1

|

1

|

1

|

0

|

0

|

1

|

The ouput toggles when J=K=1.

Answer: Option d

Answer: Option c

Answer: Option d

An instruction cycle has one or more machine cycles.

Instruction > Machine

Machine cycle time period is shorter than instruction cycle time period .

Answer: option c

Pnew = 2000 W

Answer: Option d

Answer: Option a

Answer: Option c

Answer: Option c

Pre-emption : The ability of the operating sytem to pre-empt or stop a currently scheduled task in favour of a higher priority task.

Answer: Option c

Answer: Option a

1200k + 2(450k) = 1200 + 900 = 2100kHz

Answer: Option d

Answer: Option c

Answer: option d

Answer: Option b

Answer: Option c

Answer: Option c

Anwer: Option b

First 3 choices are wrt I/o mapped I/o

Answer: Option d

Answer: Option a

Answer: Option b

Answer: Option c

Answer: Option a

Answer: Option b

Answer: Option b

Answer: Option c

Answer: Option b

Answer: Option C

Answer: Option b

Answer: Option c

Answer: Option a

Answer: Option d

Answer: Option c

Answer: Option c

Answer: Option a

Answer: Option d

Answer: Option b

Answer: Option a

Answer: Option c

Answer: Option a

Answer: Option b

Answer: Option b

Answer: Option d

Answer: Option a

Answer: Option d

Answer: Option a

Answer: Option c

Answer: Option b

Answer: Option b

Answer: Option b

Answer: Option c

Answer: Option b

Answer: Option c

Answer: Option a

Answer: Option b

Answer: Option a

Answer: Option c

Answer: Option d

Answer: Option b

This comment has been removed by the author.

ReplyDeleteIn 2011 Isro paper....I didn't understand 49 that how to answer it & in 50 how can you say -128? Plz answer.

ReplyDeletesoniakataria13@gmail.com

I think this is the way,

DeleteNo. S Data

-127 1 0000001 -> binary of +127 is 0 1111111 & its complement is 0000000 add '1' to it

-128 1 10000000 -> binary of +128 is 0 10000000 & its complement is 01111111 add '1' to it

-255 1 00000001 -> binary of +255 is 0 11111111 & its complement is 00000000 add '1' to it

-256 1 100000000 -> binary of +256 is 0 100000000 & its complement is 011111111 add '1' to it

S = Sign bit (1=-ve & 0=+ve)

Data = 2's complement

+127 has only 7 bit as data & when it is 2's complemented it can clearly visible as -ve sign bit (1)

+128 has only 8 bit as data & when it is 2's complemented it can clearly visible as -ve sign bit (1)

+255 has only 8 bit as data & when it is 2's complemented it can clearly visible as -ve sign bit (1)

+256 has only 9 bit as data & when it is 2's complemented it can clearly visible as -ve sign bit (1)

so -127&-256 are small & large to an 8 bit register. So, answer will be in remaining two.

-128 has 2's complemented data which is stored in 8 bit register is 10000000 as we know S is '1'

-255 has 2's complemented data which is stored in 8 bit register is 00000001 as we know S is '1'

In the above 2 data the largest data is representing 10000000 So, the answer is -128.

For Q 49 my explanation is,

Delete'Process' in VHDL means it is just like 'always' in verilog (Continuing repeating of loop until the case sensitive list is became stable)

CLK always changes so process block always execute.

'd' is the input data bit which is constant it may or maynot stable its our wish.

It checks condition at 'if' condition (CLK='1' indicates posedge) so the condition is checking of posedge of clock. If you have any doubt at edges of clk. check about edge triggering of clocks in google.

So, if condition is true, then it will set output 'q' as 'd' which is i/p data

and the process is end for 1 clk clock pulse.

So, we are getting a D-ff o/p for 1 clk pulse is at posedge. So, We call it as "Posedge triggered D-flipdlop"

Answer for Q 39 is a. option

ReplyDeleteCan anyone show the steps for question no 77?

ReplyDeleteThanks in advance

can you please post other isro solved papers

ReplyDeleteGreat tips, many thanks for sharing. I have printed and will stick on the wall! I like this blog. Online Courses for Mechanical Engineering

ReplyDeletecan you please explain last question

ReplyDeleteInteresting Article. Hoping that you will continue posting an article having a useful information. Waec Result Checkers Cards

ReplyDelete